반응형

이전 posting 이어서 작성.

Refrence : David Harris, Sarah Harris - Digital Design and Computer Architecture

8.4 Virtual Memory

- memory를 실제 용량보다 더욱 커보이게 만드는 방법

- Virtual address

- program은 virtual address를 사용한다.

- virtual address space는 모두 hard drive에 저장된다.

- 일부는 DRAM에 올려둔다. (DRAM부터 접근, 없으면 hard drive)

- CPU는 virtual address → physical address 로 변역하여 사용한다.

- Memory protection

- 각 program은 각자의 virtual - physical mapping을 가지고 있다.

- 두 program은 동일한 virtual address를 가질 수 있다. (physical address는 다름)

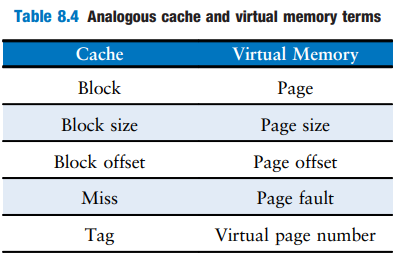

Virtual Memory Definitions

- Page size

- hard disk에서 DRAM으로 1번 이동되는 양

- Address translation

- virtual address에서 physical address로 변환

- Page table

- 변환에 필요한 table. OS가 관리

Example

Address Translation

- 19bit VPN을 15bit PPN으로 translation

- Page Offset은 그대로 내려온다. (12bit)

⇒ Virtual Address → Physical Address

How to perform translation?

- Page table을 이용한다.

- Valid bit : 1이면 page가 physical memory에 있음

- Physical page number: page가 어디 있는지 표시

Page Table Example

(1) valid

- virtual address = 0x5F20에서 VPN = 5, offset = F20

- page table에서 5번 인덱스를 찾아 PPN을 찾는다. → 0x0001

- 따라서 최종 physical address = 0x1F20

(2) invalid

- valid bit가 0이다.

- 따라서, PPN을 찾을 수 없다.

- ⇒ page table이 아닌 Disk에서 physical address를 찾아야 한다.

Page Table Challenges

- Page table은 크다.

- Load/Store 연산은 main memory로 접근을 2번 해야 한다.

- translation (page table read)

- access data (after translation)

⇒ memory의 성능은 반토막 내는 단점이 있다.

⇒ 이를 해결하기 위해 TLB을 사용한다.

Translation Lookaside Buffer (TLB)

- 최근 translation 결과를 caching한다.

- TLB에서 Hit 시 translation을 위한 메모리 접근을 안 해도 된다.

- miss시 어쩔 수 없이 메모리에 2번 접근해야 한다.

- Fully associative → Hit rate가 매우 높다. (99%) ⇒ 성공적으로 메모리 접근을 줄임

Memory Protection

- 여러 process가 동시에 동작하는데, 각 process에게는 각자의 page table이 있다.

- 각 process는 virtual address space 전체를 사용 가능하다.

- 각 process는 physical address 중에서 오직 자신의 page table에 연결된 physical address만 접근 가능하다.

- context switching → TLB를 invaildate를 시켜서 이전 page table이 TLB에 남아 있지 않도록 한다.

Virtual Memory Summary

- capacity를 높인다. 마치 더 큰 메모리가 있는 것처럼 사용 가능

- page table을 통해서 virtual address → physical address

- TLB을 사용하여 address translation의 속도를 높인다.

- memory protection → 서로 다른 process은 서로 다른 page table을 가진다.

반응형

'Computer Science > Computer Architecture' 카테고리의 다른 글

| [컴퓨터 구조] Ch8. Memory and I/O Systems(1) - Cache (0) | 2022.12.07 |

|---|---|

| [컴퓨터 구조] Ch7. Microarchitecture (0) | 2022.11.19 |

| [컴퓨터 구조] Ch6. Architecture (3) - Addressing Mode, Odds & Ends (0) | 2022.10.09 |

| [컴퓨터 구조] Ch6. Architecture (2) - Programming (0) | 2022.10.09 |

| [컴퓨터 구조] Ch6. Architecture (1) - Assembly Language, Machine Language (1) | 2022.10.08 |

![[컴퓨터 구조] Ch8. Memory and I/O Systems(2) Virtual memory](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FNx4Uq%2FbtrS5giDi8B%2FcQ8gG5v0qwjj2mosB4sMk1%2Fimg.png)