Refrence : David Harris, Sarah Harris - Digital Design and Computer Architecture

목차

- Arithmetic Circuits

- Number Systems

- Sequentail Building Blocks

- Memory Arrays

- Logic Arrays

Memory Arrays

보통 세 가지의 타입이 존재합니다.

- Dynamic random access memory (DRAM)

- Static random access memory (SRAM)

- Read Only memory (ROM)

2-dimensional array of bit cells

위 그림에서 각 bit cell에는 1 bit의 정보를 저장합니다. 그리고 한 주소 당 width만큼의 데이터를 저장하는데, 이를 word라고 합니다. 즉, 한 주소당 하나의 word를 저장하는 것이죠.

- Depth : row의 개수 (word의 개수)

- Width : column의 개수 (word의 크기)

- Array size = depth * width = (2^N) * M

- wordlind = 메모리에서의 single row, 고유한 주소를 나타낸다.

예를 들어 ‘01’이라는 주소로 접근하면 01 wordline만 1이 되고 저장된 bit가 bitline에 따라서 전송되거나 혹은 bitline에서 전송되어 받습니다. (read, write)

bitline은 우선 Z로 초기화 된 이후에 wordline이 활성화된 곳에서는 0이나 1로 업데이트됩니다.

Types of Memory

- Random access momory (RAM) : volatile

- Read only memory (ROM) : nonvolatile

1. RAM: Random Access Memory

- Volatile : 휘발성 메모리, 전원이 꺼지면 데이터가 손실된다.

- Read와 Write가 빠르다.

- Main Memory에 사용된다. (DRAM)

Random access memory는 사실 옛날 용어입니다. 옛날에 많이 사용했던 tape와 같은 저장 장치의 경우, sequential하게 data에 접근해야 합니다. 이에 반대되는 개념으로 나온 것이 Random access memory입니다. 하지만 요즘에는 모든 메모리가 random access memory이기 때문에 그 의미가 퇴색되었습니다.

2. ROM : Read Only Memory

- Nonvolatile : 비휘발성 메모리, 전원이 꺼져도 데이터가 유지된다.

- Read는 빠르지만, Write는 불가능하거나 느리다. (제조 과정에서 값이 정해져서 나온다. 요즘에는 쓰기도 가능하지만 느리다.)

- Flash memory에 사용된다.

Read Only Memory 역시 옛날 용어입니다. 예전에는 제조 당시에 값이 정해져서 나오고 더 이상 write가 불가능했지만 Flash memory와 기타 다른 ROM들은 write가 가능합니다.

Types of RAM

- DRAM (Dynamic random access) : capacitor 사용

- SRAM (Static random access memory) : cross-coupled inverter 사용

1. DRAM - Off Chip, Main Memory에 사용

DRAM은 capacitor를 이용하여 데이터를 저장합니다.

DRAM은 (1) 주기적으로, 그리고 (2) read 한 이후에 값을 refresh(rewrite) 해야 되기 때문에 Dynamic이라는 이름이 붙었습니다.

- Charge leakage from capacitor : 주기적인 refresh 필요, 시간이 지나면 전하를 잃어버려 data를 잃는다.

- Reading destroy the stored value : 한 번 읽은 data는 다시 write 해줘야 함

- 비교적 단순한 구조라서 집적도가 높고 가격이 싸다. (트랜지스터 1개 필요)

capacitor에 전하가 차 있으면 1을, 없으면 0을 나타낸다.

WordLine=1, BitLine=1라면, ⇒ Cap=charge -> data '1'을 write,

WordLine=1, BitLine=0라면, ⇒ Cap=discharge -> data '0'을 write

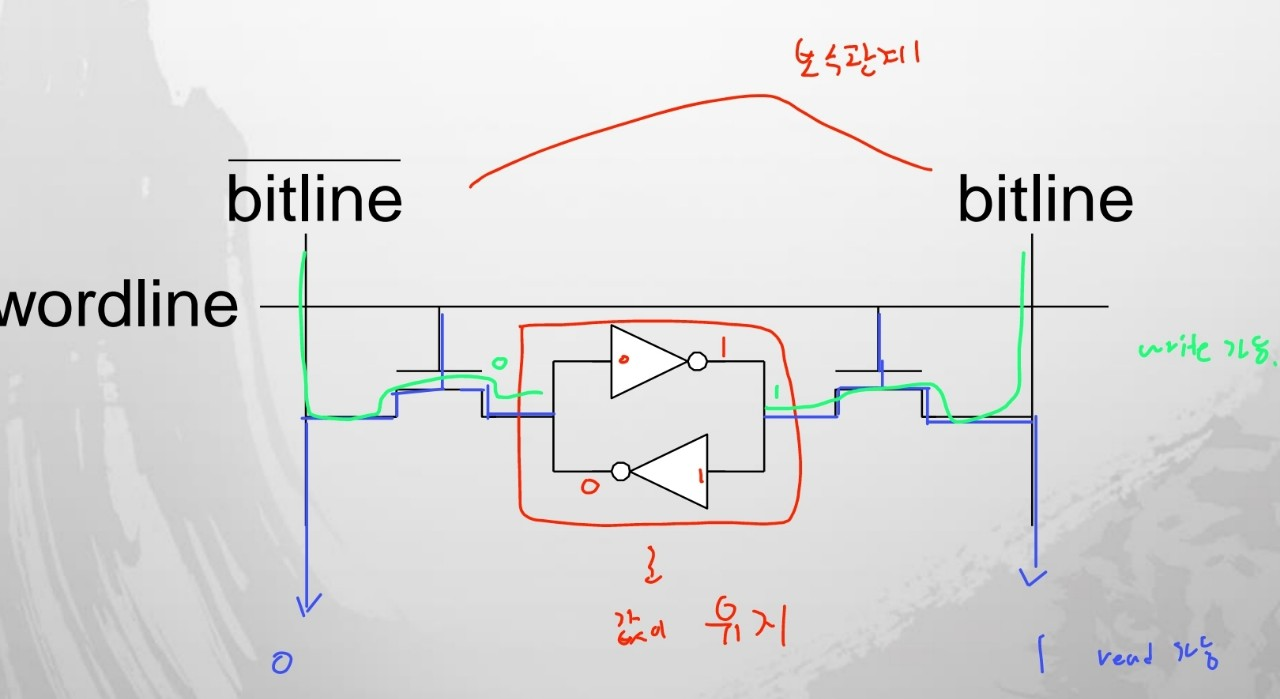

2. SRAM - On Chip, Cache에 사용

SRAM은 cross-coupled inverter를 사용하여 데이터를 저장합니다.

또한 refresh할 필요가 없기 때문에 ‘static’합니다.

- static : refresh 할 필요가 없다.

- 회로가 비교적 복잡하여 집적도가 낮고 가격이 비싸다. (트랜지스터 6개 필요)

- 소용량의 메모리나 캐시 메모리에 사용된다.

예를 들어 BitLine에 High(1) 신호가 들어오면, 인버터를 통해서 1과 0이 값을 계속 유지할 수 있습니다.

SRAM의 write 과정을 살펴보면,

- WL에 1을 입력하여 해당 셀을 선택한다.

- BL에 1을, NOT BL에 0을 입력하면 전원이 들어가 있는 한 계속 같은 상태를 유지한다.

- 이 상태에서 WL을 0으로 만들면 두 TR는 Off가 되어 새로운 데이터가 들어가지 않는다.

⇒ 즉, 0과 1이라는 데이터를 계속 유지할 수 있다.

이처럼 SRAM은 DRAM 과 달리 주기적으로 refresh를 해 줄 필요가 없습니다.

SRAM의 read 과정을 살펴보면,

- WL에 1을 입력하여 해당 셀을 선택한다.

- 양쪽의 TR이 On이 되어 인버터의 출력이 각각의 bit line으로 나가게 된다.

DRAM vs SRAM

ROM : Dot Notation

아래와 같이 점을 찍어서 ROM을 나타내는 방법입니다.

진리표를 통해서 Data를 구하면,

Data0 = A1 inverse * A0 inverse

Data1 = A1 inverse + A0

Data2 = A1 XOR A0

Example : Logic with ROMS

Logic with Any Memory Array

Lookup Table

룩업테이블은 주어진 연산에 대해 미리 계산된 결과들의 집합(배열)을 가리킵니다.

Multi-ported Memories

- Port : address/data pair

- Register file : small multi-proted memory

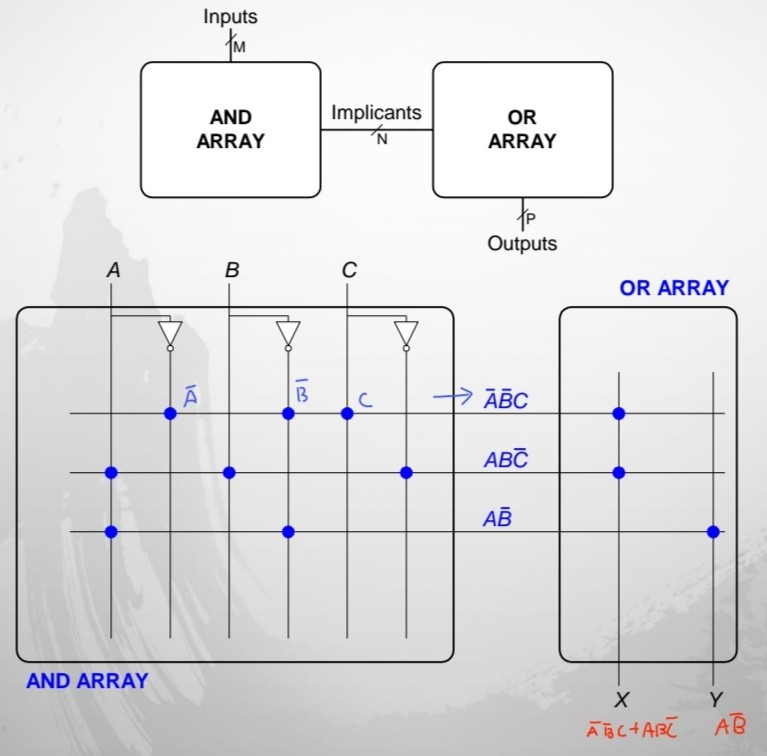

Logic Arrays

PLAs (Programmable logic arrays)

- And gate로 연결된 array들을 OR로 연결 (Sum of Product, SOP)

- Combinational logic only

- Fixed internal connections

FPGAs(Field programmable gate arrays)

- Arrays of Logic Elements (LEs)

- Combinational and sequentail logic

- Programmable internal connections

PLAs

Example

위와 같이 AND Array을 통해서 주어진 식을 완성한 다음에 OR Array로 연결하면 됩니다.

FPGA : Field Programmable Gate Array

FPGA는 프로그램 가능한 논리 소자의 배열의 일종입니다.

다음의 요소로 구성됩니다.

- LEs (logic elements ) : perform logic

- IOES (Input/output elements) : 외부와 연결되는 interface

- Programmable interconnection : LEs와 IOEs 연결

LE : Logic Element

- LUTs (lookup table) : perform combinational logic

- Flip-flops : perform sequential logic

- Multiplexers : LUT와 Flip-flop 연결

FPGA Desing Flow

- Enter the design : hdl로 코딩하여 설계하여 디자인한다.

- Simulate the design and map it onto FPGA : 시뮬레이션으로 디자인을 검증한다.

- Download the configuration onto the FPGA : 유저가 구현한 High-Level한 디자인을 FPGA보드가 이해할 수 있는 Low Level로 바꾼다.

- Test the Design

![[컴퓨터 구조] Ch5. Digital Building Blocks (3) - Memory Arrays, Logic Arrays - ROM, DRAM, SRAM 중점으로](https://img1.daumcdn.net/thumb/R750x0/?scode=mtistory2&fname=https%3A%2F%2Fblog.kakaocdn.net%2Fdn%2FBcTYg%2FbtrM0ntai7O%2F0f3oVVqGbwJrCWWKjQpBdk%2Fimg.png)